从MOSFET到FinFET再到GAAFET,每当摩尔定律遭遇困境,总会有新的技术及时出现并引领着摩尔定律继续前行。不同芯片巨头也在不同制程下争相加码新工艺。

那么,这三大工艺对比优点和缺点分别有什么?如何推动着工艺制造的发展?

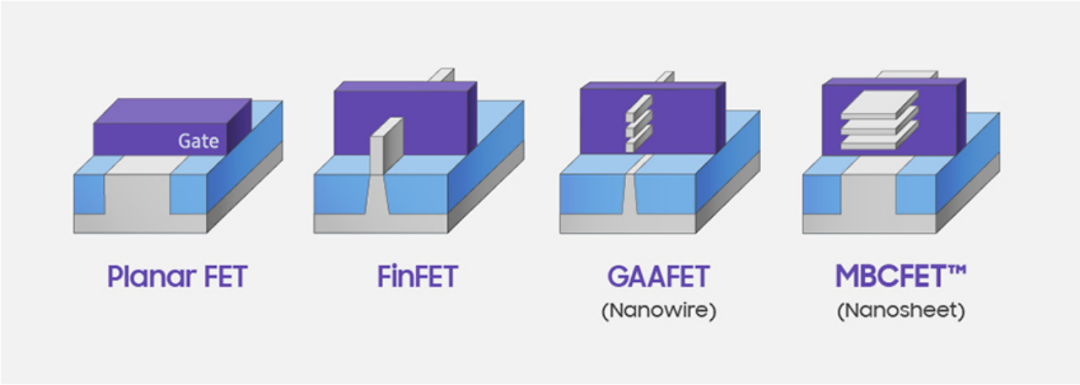

MOSFET-FinFET-GAAFET结构对比

从结构来看,平面MOSFET只能在闸门的一侧控制电路的接通与断开,但是在FinFET架构中,闸门被设计成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流,同时让晶体管的闸长大幅度缩减。

英特尔在FinFET工艺上率先出手,在2011年推出商业化的FinFET工艺技术,之后台积电也迅速跟进,在16nm节点中使用了FinFET。从16/14nm开始,FinFET成为半导体器件的主流选择。三星则是在2015年的14nm才开始使用。

不过FinFET工艺的极限是7nm制程,可是在如今的3nm制程研发中,三星选择的是GAAFET工艺,而台积电依旧坚持FinFET,那么为什么说7nm是FinFET的物理极限?

从10年前的芯片制程来看,当时不少人认为65nm制程中二氧化硅绝缘层漏电已经到了无法容忍的地步,后来工业界引入了HKMG,用High-K介质取代了二氧化硅。随后工艺发展到22nm,其沟道关断漏电到达极致,工业界又发明了FinFET和FD-SOI,前者用立体结构取代平面器件来加强栅极的控制能力,后者用氧化埋层来减少漏电。

而说7nm制程是FinFET的物理极限,是因为到了7nm节点即使是FinFET也不足以在保证性能的同时抑制漏电。至于FinFET在更先进制程的使用是因为有极紫外光刻机以及砷化铟镓的加持,这也印证了为什么MOSFET可以坚持到20nm。

到了5nm节点后,虽然已经使用上了EUV光刻技术,但是基于FinFET结构进行的芯片尺寸的缩小,就变得更加困难。鳍片距离太近、漏电重新出现,再加上鳍片增高的高度越来越高,难以保持直立结构,以及物理材料的极限都让 3D FinFET 晶体管难以为继。

FinFET走向极限时,延续半导体技术经典“摩尔定律”的新兴技术路线的新技术GAAFET问世。

GAAFET问世

GAAFET即环绕栅极场效应晶体管,其结构晶体管的本质,就是把FinFET的Fin旋转90°,然后把多个Fin横向叠起来,这些Fin都穿过gate。随着GAAFET晶体管的gate(门)与channel(沟道)的接触面积变大,而且对于FinFET而言,Fin的宽度是个定值;但对GAAFET而言,sheet(薄片)本身的宽度与有效沟道宽度是灵活可变的。更宽的sheet自然能够达成更高的驱动电流和性能,更窄的sheet则占用更小的面积自然可以提供比FinFET 更好的静电特性,满足某些栅极宽度的需求。

在同等尺寸结构下,GAAFET 的沟道控制能力强化,尺寸进一步微缩更有可能性,且新的结构所需的生产工艺应该与鳍式晶体管相似,可以继续使用现有的设备以及技术成果;栅极与通道之前的接触面积更大,新的结构带来的寄生电容和电阻问题应得到显著改善。

GAAFET有两种结构,一种是使用纳米线(Nanowire)作为电子晶体管鳍片的常见GAAFET;另一种则是以纳米片(Nanosheet)形式出现的较厚鳍片的多桥通道场效应管MBCFET,这两种方式都可以实现3nm工艺节点,只是取决于制造商具体的设计。从GAAFET到MBCFET,可以视为从二维到三维的跃进,能够改进电路控制,降低漏电率。

其中MBCFET 相比纳米线技术拥有更大的栅极接触面积,从而在性能、功耗控制上会更加出色。三星表示传统的 GAAFET 工艺采用三层纳米线来构造晶体管,栅极比较薄,而三星 MBCFET 工艺使用纳米片构造晶体管,三星声称其 MBCFET 可以提供更低的工作电压、更高的电流效率(即驱动电流能力)和高度的设计灵活性。不过MBCFET 是最易制造的一种,虽然它能承载更大电流,但栅控能力不够纳米线强。

2018年三星公布了被称为多沟道FET(multi-bridge-channel FET,MBCFET)的环绕栅极工艺,事实上多年之前就开始了研发。在2017年的VLSL technology symposium会议上,IBM就发表了与三星和Global Foundries合作研发5nm GAA晶体管。三星表示,其新的3nm MBCFET可减少面积35%,同等功耗下性能提升30%,同等性能下功耗降低50%。

台积电的3nm则继续沿用FinEFT技术,主要是考量客户在导入5nm制程的设计也能用在3nm制程中,他们还表示在2nm的制程研发中将会采用GAAFET架构;英特尔也在努力在2024-2025年使用它们。

几大架构相比,FinFET仍占主流

新架构的工艺控制难

GAAFET作为新架构,制造工艺复杂。GAAFET的制造流程,首先在substrate(衬底)上沉积超薄的锗化硅与硅的交替层,形成一种超晶格结构(super-lattice),每种材料叠多层。sheet就是在超晶格结构中曝光与蚀刻的。随后内部spacer(隔板)隔层构成;在spacer蚀刻时,超晶格结构中,锗化硅层的表面部分凹陷,再填入介电材料。随后源极漏极形成,超晶格结构中的锗化硅层移除,留下硅基层sheet,也就是channel沟道。最后,通过沉积high-k(高介电常数)的介电与金属gate材料来构成gate。每一步都存在相当多的工程问题,也就要求工厂有完美的工艺流程控制策略。材料供应商Brewer Science说越小的节点,工艺控制存在的挑战就越大。在3nm节点以后,EUV光刻、原子层沉积(atomic layer deposition)、检测与量测等等技术都需要持续进化。

综合成本高

从成本和性能角度来看,GAAFET确实可以提供更高的性能,但同时也带来了更高的成本。此前台积电就谈到过,3nm节点应用FinFET,能够降低风险,客户不需要迁移到新的晶体管类型就能开展3nm芯片的设计工作。三星也透露其自家 3nm GAA 的研发成本比 5nm FinFET 高得多,有可能超过 5 亿美元,巨大的研发成本首先就是摆在行业面前的一道坎。

加之芯片的制程已发展到2nm,工艺愈发先进突破越困难,时间也越久,如此看来FinFET的应用面远远多于GAAFET,FinFET与GAAFET暂时也不存在谁取代谁的问题。